数字化工业软件

# 未来已来，你准备好了吗？

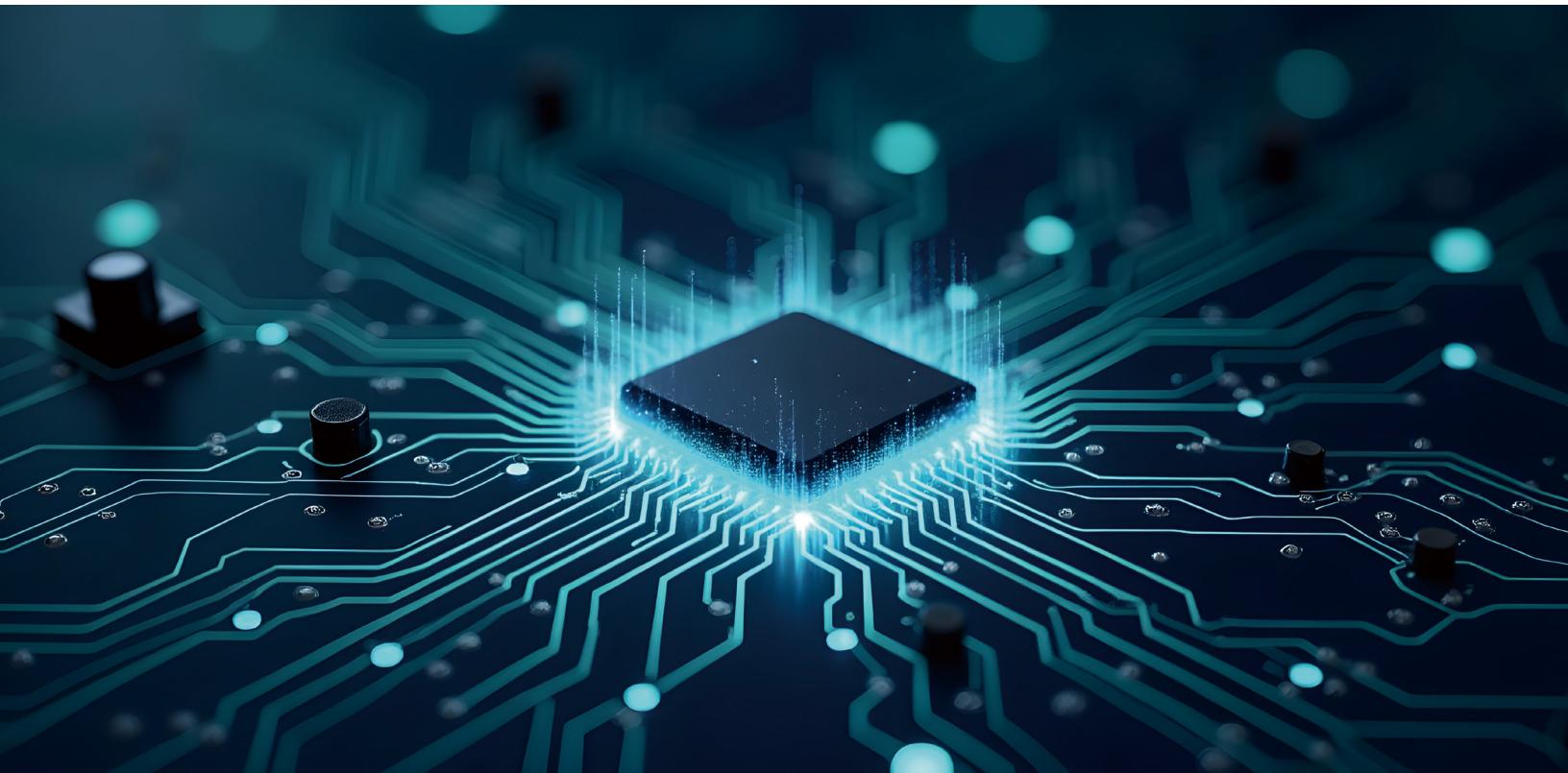

软件定义、AI 加持、芯片赋能的电子产品正在重塑半导体行业

## 内容摘要

随着半导体设计空前复杂，AI 技术工作负载对算力的需求不断增长，传统的芯片设计和验证方法正在被彻底重塑。本白皮书探讨了数字孪生、小芯片 (Chiplets) 和 AI 技术的融合如何创造新的可能性，同时旨在解决半导体行业长期面临的挑战。

# 半导体行业格局之变

半导体行业正处于其发展历程中的关键时刻。长期以来，电子设计自动化(EDA)一直是芯片设计和验证的中坚力量，如今，在AI技术、设计复杂性日益提高，小芯片、3D IC设计、系统级封装和系统级芯片等新型架构范式涌现，以及AI技术高性能、高需求计算需求的推动下，EDA正在经历一场根本性的变革。到2030年，半导体中AI技术的增长预计将达到35%——约70%的半导体将服务于AI技术。该行业面临着前所未有的挑战，但也蕴藏着机遇，全球半导体行业预计将超过1.2万亿美元。(来源：International Business Strategies, 2025年2月至2026年)

随着对更精细、更高效、更快技术的需求日益增长，传统方法已无法应对新的挑战，而这些方法自身也已临近极限。集成电路(IC)和先进IC封装的设计、制造和实施复杂性呈指数级增长，形成了行业专家所称的“半导体工程鸿沟”。电子、机械和软件工程师们再也无法局限于各自的设计领域，独立地工作。要打造现代电子产品，就必须依靠多领域协同的解决方案，使工程师从设计初期就能够以集成的方式展开协作，并在整个开发过程中始终保持这种集成。

半导体行业是国际化的——原材料几乎来自全球各地。在全球化的贸易经济下，获取原材料和制造服务的考量因素变得愈发复杂。基于当前环境，如何以及在何处将产品交付给客户的电路板和系统构建地点，对于持续的业务运营而言并非小事。可以肯定地说，当今的半导体行业正面临着多重相互关联的挑战，而这些挑战与过去几十年的挑战截然不同。

# 同而不同

自集成电路 (IC) 制造之初，工程师们就一直在应对复杂性。无论是当前还是未来的需求，以及不断变化的期望，都在持续增加这种复杂性。半导体设计工程师还面临着同时优化多个因素的问题，例如：

## 热耗散：

确保芯片产生的热量能够得到有效管理和散热，以防止过热和故障。

## 信号完整性：

在信号通过芯片时保持其完整性，防止数据损坏，确保通信可靠。

## 电源完整性：

确保芯片的电源供应稳定且一致，防止可能干扰操作的电源波动。

## 机械可靠性：

设计芯片以承受其在运行过程中将遇到的机械应力，从而防止物理故障。

## 逻辑性能：

优化芯片的逻辑操作，以确保其高效准确地执行预期功能。

## 集成挑战

随着设计逐渐转向基于小芯片的架构和 3D 集成方向发展，以满足日益增长的需求负载，工程师们面临着新的挑战。他们需要：

- 确保小芯片之间能够有效通信，保持高性能和高带宽。

- 开发先进封装技术以支持多个小芯片的集成和 3D 堆叠。

- 管理堆叠芯片产生的热量，以防止过热并确保可靠运行。

- 确保信号和电源在多个芯片之间得以维持，防止数据损坏和电源波动。

## 软硬件融合

AI 技术框架开发和计算模型的快速发展，对性能和功率提出了更高要求，这增加了新设计中的复杂性。例如：

- 管理每个核心的多个软件栈，确保兼容性并优化性能。

- 确保硬件和软件能够无缝协作，防止出现可能中断操作的兼容性问题。

- 优化并确保不同组件高效协同工作。

这些挑战，有些是熟悉的，有些则是未知的或尚待探索的。它们都将需要创新的方案、周密的规划和尖端的技术，以确保先进半导体设计的可靠性和性能。

# 电子设计自动化的新方法

电子设计自动化 (EDA) 行业已从最初的简单电路设计工具获得日新月异的发展。如今的 EDA 硬件和软件设计与验证系统需要帮助工程师应对这些挑战。

EDA 工具必须能够对芯片在多个物理领域(包括电气、机械和热学)的行为进行多物理场仿真。它们必须确保工程师能够可靠且自信地使用 AI 技术技术来优化设计和验证流程，从而提高效率和准确性。它们也必须支持先进封装设计，以集成多个小芯片和实现 3D 堆叠。当今的 EDA 工具必须为整个系统的性能和可靠性提供卓越的系统级验证，确保所有组件无缝协作。最后，它们还必须具备集成数字孪生的能力，从实现从设计到制造及后续流程的虚拟原型制作、仿真和闭环反馈。

先进的功能将使工程师能够应对现代半导体设计日益增长的复杂性，确保其产品的可靠性和性能。正是这类解决方案将在软件驱动设计、小芯片和先进 3D IC 等领域引领集成电路 (IC) 的未来发展方向。

## 软件驱动的硬件设计

传统的先设计硬件再适配软件的方法，已被现代计算的需求所颠覆，尤其是在人工智能以及超大规模计算、医学研究、航空航天、汽车与交通运输开发、下一代通信和新能源技术等行业的高性能应用领域——甚至游戏和金融系统也在向这一领域进发。软件驱动的设计代表了半导体系统构思和实现方式的根本转变，能够满足日益增长的数据管理和计算工作负载需求。

软件工作负载现在从设计的最初阶段就在影响硬件架构决策——这一转变在以 AI 技术为中心的应用中尤为明显。随着 AI 技术快速向通用人工智能 (AGI) 发展，软件工作负载的数量和多样性正在急剧攀升。这种激增带来了重大的能源瓶颈——不仅是由于不断增长的算力需求，还因为当前系统处理这些工作负载的方式效率低下。通用硬件已无法维系这一发展轨迹。为了满足未来 AI 系统的需求，我们需要一种由软件设计驱动、由运行在其之上的软件工作负载优化的硬件设计，使我们能够为底层架构量身定制，以实现最高的效率和性能。

## 小芯片架构的兴起

小芯片(Chiplets)已成为一项关键解决方案, 原因如下: 小芯片能够在先进节点中实现更高效的电源分配和更好的良率管理, 从而克服了 SoC 设计的局限性。它们支持更高效的电源分配, 从而实现了先进封装和 3D 堆叠。最后, 它们支持更多的 IP 复用, 能够集成经过验证的 IP 模块, 提高复杂半导体设计的可靠性和性能, 并支持计算能力扩展。

当然, 转向基于小芯片的设计也带来了工程师必须解决的新复杂性。他们需要确保小芯片之间能够高效通信, 保持高性能和高带宽。他们需要管理多个芯片间的功耗需求, 并防止可能扰乱操作的功率波动。必须控制堆叠 Dies 产生的热量, 以防止过热并确保可靠运行。他们还需要确保跨管芯边界保持信号, 以防止数据损坏和功率波动。

# 全面数字孪生：基于虚拟原型实现经验证的物理仿真

数字孪生已成为半导体设计和制造中的重要工具。它们实现了物理资产的虚拟、动态同步表示，提供实时监控和优化能力。数字孪生支持实时监控和优化能力，提高效率和准确性，并且它们能够集成电气、机械和热分析，确保了可靠性和性能。

在半导体设计中使用数字孪生为工程师带来了切实益处，例如：通过仿真驱动优化更快实现更高良率；增强可追溯性和零缺陷管理；动态规划和调度能力；以及实时问题诊断和异常检测。所有益处都有助于提高效率、准确性、可靠性和性能。

数字孪生模型越全面地代表物理产品、过程或操作，它就越能准确地预测现实世界的性能。

西门子提供全面、基于物理的数字孪生模型，可覆盖产品或工艺流程的整个生命周期。全面数字孪生是由横跨 IT 和 OT 的软硬件组合实现的，能够将研发和工程与制造、供应链和运营联系起来。

借助全面数字孪生，半导体公司可以确保对分立式、配方化以及软件驱动的产品的设计、制造工艺和系统性能进行持续、自动化的改进。

# 集成 AI 技术以变革设计与验证

AI 技术正在彻底改变半导体设计的方方面面，尤其是在优化和增强工作流程方面。例如，AI 技术能够实现：

- 验证中的自动化模式识别。

- 海量仿真数据的高效分析。

- 智能数据管理和分析。

- 将 AI 技术与基于物理的仿真相结合的混合仿真。

- 通过机器学习提升设计人员生产力并加速设计空间探索。

- 改善良率优化的预测分析。

- 复杂设计场景中的自动化决策。

正如行业专家 Ed Sperling 在《半导体工程》(Semiconductor Engineering) 中所说：“当你在一个工作负载复杂的模拟器上运行一个包含 100 亿个门级的设计时，你所面对的是数千亿个周期，因此而产生的数据过于庞大，我们需要使用 AI 技术来有效地检测需要检测的内容，并调整需要分析的内容。”

# 你为即将到来的变革做好准备了吗？

半导体行业在 3D IC 设计中面临着日益增长的复杂性。例如，对 AI 优化架构的需求预计只会增加。随着安全要求的提高，能效也可能变得越来越重要。技术趋势也在变化，要求工程师们必须适应——例如，先进封装技术、新型互连解决方案、改进热管理技术的需求以及对增强配电网络的要求。所有这些都将需要先进的技术和创新的解决方案。

西门子 EDA 具备独特的优势，能够与客户合作，为现代半导体设计的设计和验证创造先进的解决方案：

- 集成 AI 技术和数字孪生技术。

- 先进的多物理场仿真能力，支持跨多个物理领域的全面仿真和分析。

- 强大的生态系统。

- 行业领先的工具集成。

我们持续致力于推进 AI/ML、数字孪生技术及验证方法，同时扩展我们的合作伙伴生态体系。例如，Innovator3D IC 是一个统一平台，专为 3D IC 和基于 Chiplet 的半导体设计提供规划、原型设计与预测性分析，支持异构集成平台的开发。凭借我们对 PCIe 和 BoW 等行业标准的强有力支持，我们可以帮助确保 Chiplet IP 的无缝集成，以推动先进封装和 3D 堆叠。同时，我们也深知多物理场先进分析能力的重要性，能够在多个领域实现全面的仿真与分析支持。

半导体行业正处于关键时刻，传统方法亟需演进，以应对新的挑战。软件驱动的设计、小芯片、数字孪生与 AI 技术的融合，正在带来前所未有的创新机遇，同时也引入了必须仔细应对的新复杂性。西门子 EDA 支持的全面数字孪生，融合了贯穿整个半导体生命周期的先进工具与深厚的行业专业知识，使我们成为企业应对这一变革格局中不可或缺的重要合作伙伴。

## 我们随时准备提供帮助

制造未来的产品需要一个支持开放和互联开发与验证的生态系统。当今技术所代表的软件定义、AI 加持、芯片赋能的系统体系，需要最全面数字孪生来实现。西门子深知，推动产品差异化与价值提升的核心，始于软件、半导体与电子系统。凭借数十年的行业经验，我们将持续研发并投入端到端的 EDA 解决方案，帮助客户取得成功。

## 西门子数字化工业软件

美洲: 1 800 498 5351

欧洲、中东和非洲: 00 800 70002222

亚太: 001 800 03061910

如需其他电话号码, 请点击 [此处](#).

**西门子数字化工业软件** 通过 Siemens Xcelerator 开放式数字商业平台的软件、硬件和服务, 帮助各规模企业实现数字化转型。西门子的工业软件和全面数字孪生可助力企业优化设计、工程与制造流程, 将创新想法变为可持续的产品, 从芯片到系统, 从产品到制造, 跨越各个行业, 创造数字价值。 [Siemens Digital Industries Software](#)

- Accelerating transformation.